# COMPLEXITY REDUCTION IN DISCRETE EVENT SYSTEMS

BY

## RAJINDERJEET SINGH MINHAS

A thesis submitted in conformity with the requirements for the degree of Doctor of Philosophy, Graduate Department of Electrical and Computer Engineering, in the University of Toronto.

$\begin{array}{c} \mbox{Copyright} \textcircled{C} 2002 \ \mbox{by Rajinderjeet Singh Minhas.} \\ \mbox{All Rights Reserved.} \end{array}$

For my parents.

## Complexity Reduction in Discrete Event Systems

Doctor of Philosophy Thesis Edward S. Rogers Sr. Department of Electrical and Computer Engineering University of Toronto

> by Rajinderjeet Singh Minhas September 2002

# Abstract

The aim of this thesis is to explore new ways to achieve complexity reduction in discrete event systems (DES). We present three different ways of reducing complexity. First, we present a symbolic supervisory control design method for composite systems such that the complete state space never needs to be computed. Instead of a supervisor implemented by a static lookup table, we provide a function that can be efficiently and dynamically computed at each state to determine the control action. This symbolic function can be suitably modified to ensure that the system under control is free of deadlocks. Secondly, we present a heuristic algorithm to reduce the size of a (static) supervisor. Our symbolic supervision scheme is not able to guarantee non-blocking behaviour in the system under control. So to ensure non-blockingness it may be necessary to use a lookup table. Finding the smallest lookup table for a given control task is an NP-hard problem. We propose a greedy supervisor reduction algorithm based on the concept of control covers. This algorithm seems to work quite well in a large number of cases. Finally, we present a compact model of timed discrete event systems (TDES). We use local timers at each state of the TDES to model the passage of time. This model is quite robust to changes in time scale and is closed under control.

## ACKNOWLEDGEMENTS

First and foremost, I want to thank Prof. Wonham for everything he has done for me over the years. Without a doubt, this work would not have been possible without his keen mathematical insight, guidance and financial support. However, I am most grateful for his counsel on things totally unrelated to this work.

I would also like to thank Dr. Bertil Brandin and Dr. Meera Sampath for the internship opportunities at Siemens and Xerox respectively. The experience I gained during these internships has been invaluable.

The students, faculty and staff at the System Control Group have been incredibly helpful and gracious over the years and for that I am very thankful. In particular, Peyman Gohari and Sean Bourdon have been a pleasure to know and work with.

Finally, I would like to thank the University of Toronto and the government of Ontario for the financial assistance they provided in the form of fellowships. Sarah Cherian went out of her way to help me and I am grateful for that.

# Contents

| Α  | bstra            | ct                                 | ii   |  |  |

|----|------------------|------------------------------------|------|--|--|

| A  | Acknowledgements |                                    |      |  |  |

| Li | ist of           | Tables                             | viii |  |  |

| Li | ist of           | Figures                            | xii  |  |  |

| 1  | Intr             | oduction                           | 1    |  |  |

|    | 1.1              | Goal and the Main Results          | 2    |  |  |

|    | 1.2              | Related Work                       | 3    |  |  |

|    |                  | 1.2.1 Symbolic Supervision         | 4    |  |  |

|    |                  | 1.2.2 Supervisor Reduction         | 6    |  |  |

|    |                  | 1.2.3 Timed Discrete Event Systems | 7    |  |  |

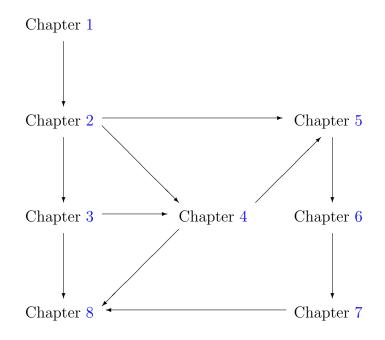

|    | 1.3              | A Roadmap for the Thesis           | 9    |  |  |

| 2  | Not              | ation                              | 12   |  |  |

|    | 2.1              | An Overview                        | 12   |  |  |

|    | 2.2              | Notation and Definitions           | 13   |  |  |

|    |                  | 2.2.1 Distribute and Join          | 20   |  |  |

|    |                  | 2.2.2 Controllability of Automata  | 27   |  |  |

| 3 | Symbolic Supervision |                                                 | 32  |  |  |

|---|----------------------|-------------------------------------------------|-----|--|--|

|   | 3.1                  | An Overview                                     | 32  |  |  |

|   | 3.2                  | Modular Checking of Controllability             | 34  |  |  |

|   | 3.3                  | Synthesis of Supremal Controllable Subautomaton | 38  |  |  |

|   | 3.4                  | Deadlock Avoidance                              | 51  |  |  |

|   |                      | 3.4.1 Some Comments                             | 72  |  |  |

|   | 3.5                  | Complexity Analysis                             | 73  |  |  |

|   |                      | 3.5.1 Complexity without Deadlock Avoidance     | 74  |  |  |

|   |                      | 3.5.2 Complexity with Deadlock Avoidance        | 75  |  |  |

|   | 3.6                  | Summary                                         | 76  |  |  |

| 4 | Supervisor Reduction |                                                 |     |  |  |

|   | 4.1                  | An Overview                                     | 77  |  |  |

|   | 4.2                  | Implementation of a Supervisor                  | 78  |  |  |

|   | 4.3                  | Control Covers and Supervisor Reduction         | 80  |  |  |

|   | 4.4                  | An Algorithm for Finding a Control Cover        | 83  |  |  |

|   | 4.5                  | Estimation of the Size of a Minimal Supervisor  | 101 |  |  |

|   | 4.6                  | Summary                                         | 106 |  |  |

| 5 | More Notation        |                                                 |     |  |  |

|   | 5.1                  | An Overview                                     | 107 |  |  |

|   | 5.2                  | Notation for Timed Discrete Event Systems       | 108 |  |  |

| 6 | Sho                  | ortest and Longest Paths in a TTG               | 125 |  |  |

|   | 6.1                  | An Overview                                     | 125 |  |  |

|   | 6.2                  | Shortest Paths                                  | 126 |  |  |

|   |     | 6.2.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Postfix Solution to the Shortest Path Problem | 130 |

|---|-----|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------|-----|

|   |     | 6.2.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Prefix Solution to the Shortest Path Problem  | 132 |

|   | 6.3 | Longes                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | st Paths                                      | 133 |

|   |     | 6.3.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Postfix Solution to the Longest Path Problem  | 134 |

|   |     | 6.3.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Prefix Solution to the Longest Path Problem   | 135 |

|   | 6.4 | Orderi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ng of Strings and Timer Matrices              | 138 |

|   |     | 6.4.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A Postfix Total Order on Strings              | 139 |

|   |     | 6.4.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A Prefix Total Order on Strings               | 142 |

|   |     | 6.4.3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | A Partial Order on Timer Matrices             | 142 |

|   | 6.5 | Prefix                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | versus Postfix Solution                       | 148 |

|   |     | 6.5.1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Ease of Computation                           | 148 |

|   |     | 6.5.2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Usefulness for Supervisory Control            | 149 |

|   | 6.6 | A Cou                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | inter-example                                 | 151 |

|   | 6.7 | Summ                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | ary                                           | 157 |

| 7 | AN  | and the formation of th | of Timed Discrete Event Systems               | 158 |

|   | 7.1 | Motiva                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ation                                         | 158 |

|   | 7.2 | An Ov                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | verview                                       | 165 |

|   | 7.3 | Timed                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | Generators                                    | 165 |

|   | 7.4 | Contro                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ollability and Supervision                    | 173 |

|   | 7.5 | Suprer                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | nal Controllable Sublanguages                 | 179 |

|   | 7.6 | Tempo                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | oral Specifications                           | 182 |

|   | 7.7 | Closur                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | e Of Timed Generators Under Control           | 185 |

|   | 7.8 | Deriva                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | tion of a TG from an ATG                      | 190 |

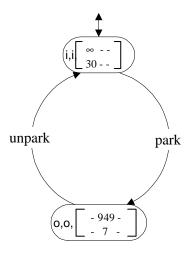

|   | 7.9 | Synchi                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | ronous Composition of Timed Generators        | 197 |

|    | 7.10 Design Examples Using Timed Generators | 198 |  |

|----|---------------------------------------------|-----|--|

|    | 7.11 Summary                                | 207 |  |

| 8  | Conclusions                                 | 208 |  |

|    | 8.1 Limitations and Future Research         | 210 |  |

| Α  | Some Proofs                                 | 212 |  |

|    | A.1 Proof of Theorem 104                    | 212 |  |

|    | A.2 Proof of Theorem 105                    | 216 |  |

| в  | Synchronous Composition of Timed Generators | 221 |  |

| Bi | Bibliography                                |     |  |

| In | Index (including Symbols and Abbreviations) |     |  |

# LIST OF TABLES

| 3.1 | Computation Times for the Symbolic Supervision of Small Factory | 51 |

|-----|-----------------------------------------------------------------|----|

| 4.1 | Typical Results of the Supervisor Reduction Algorithm           | 97 |

# LIST OF FIGURES

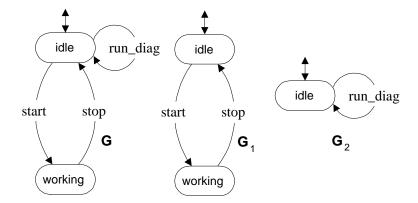

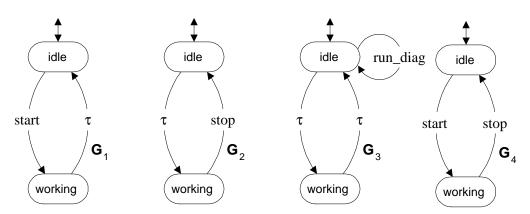

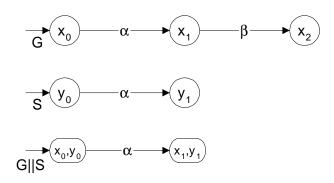

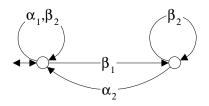

| 2.1  | Partial Models of a Machine                                                  | 20 |

|------|------------------------------------------------------------------------------|----|

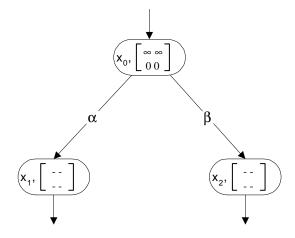

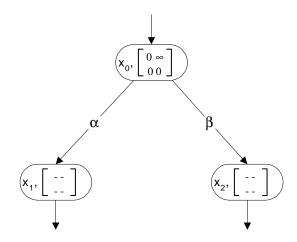

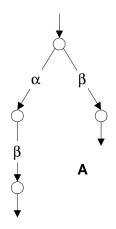

| 2.2  | Distribution of an Automaton                                                 | 24 |

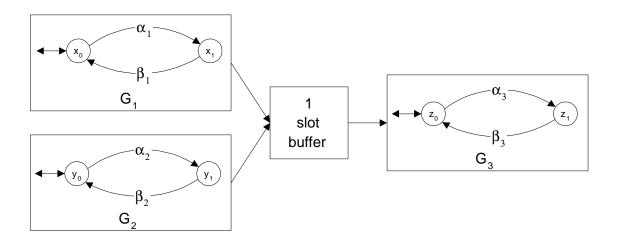

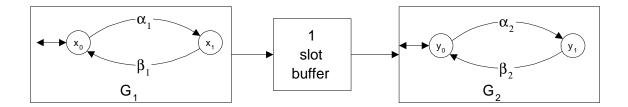

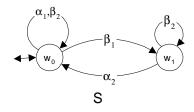

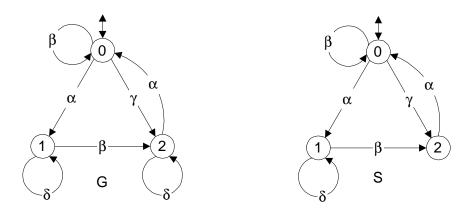

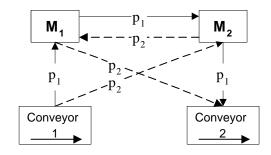

| 3.1  | Small Factory                                                                | 37 |

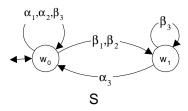

| 3.2  | Buffer under/overflow specification                                          | 37 |

| 3.3  | Distributed buffer specifications                                            | 38 |

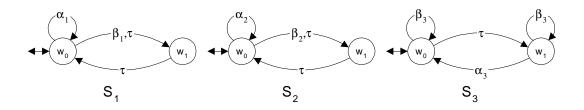

| 3.4  | Synchronous product of distributed specifications with respective plant com- |    |

|      | ponents                                                                      | 38 |

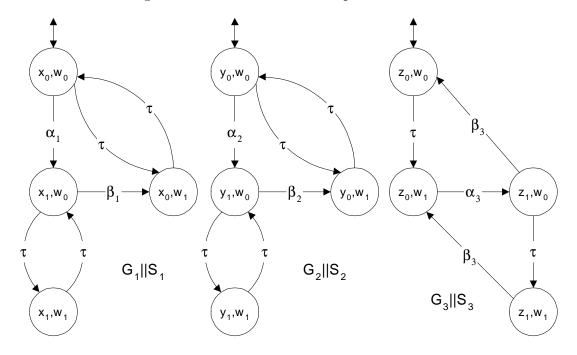

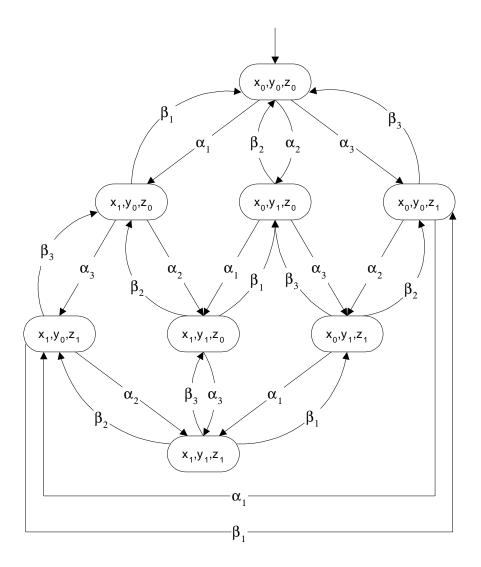

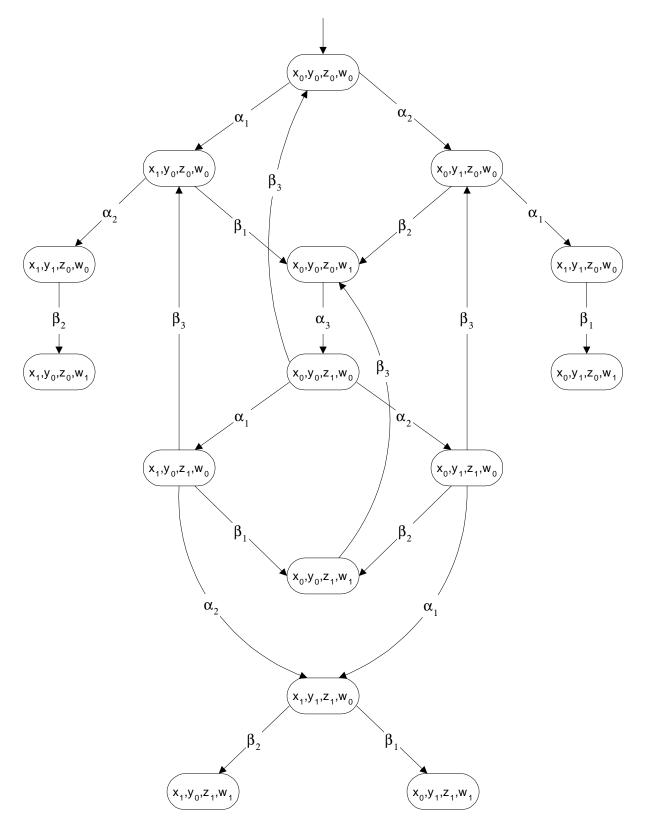

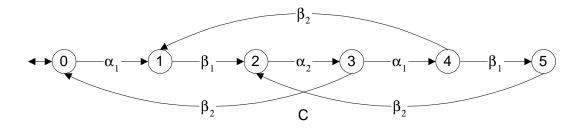

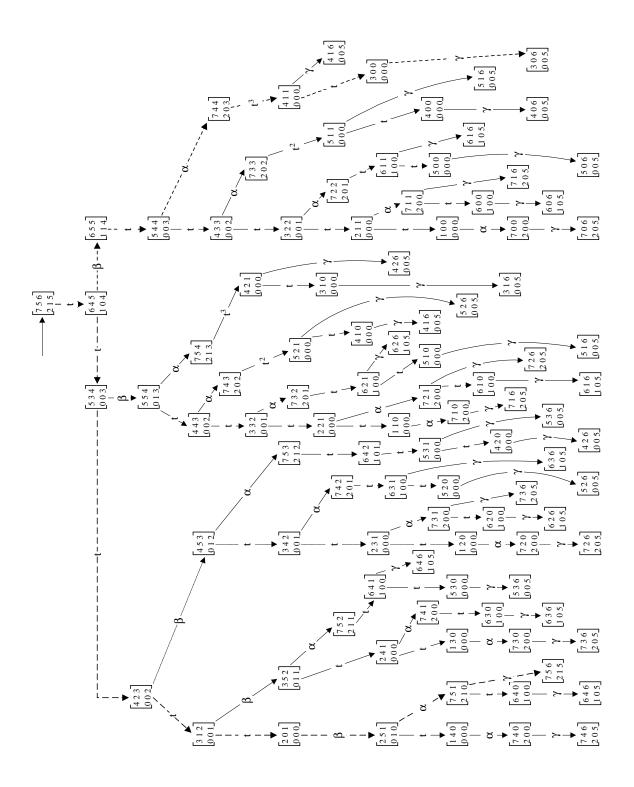

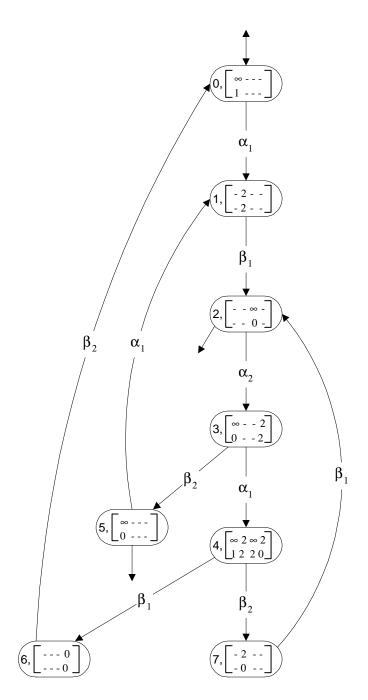

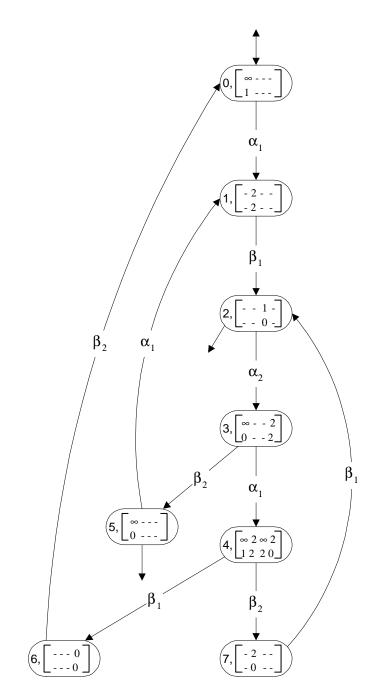

| 3.5  | $\mathbf{G}_1 \  \mathbf{G}_2 \  \mathbf{G}_3$                               | 48 |

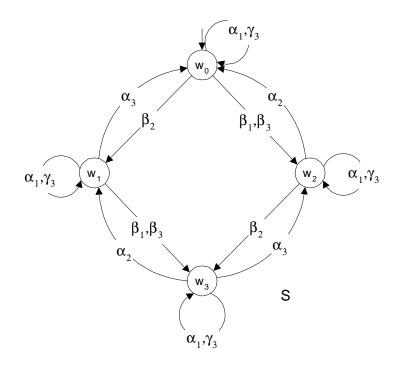

| 3.6  | $\mathbf{G}_1 \  \mathbf{G}_2 \  \mathbf{G}_3 \  \mathbf{S}$                 | 49 |

| 3.7  | Blocking versus Deadlock Detection                                           | 52 |

| 3.8  | Blocking versus Deadlock Detection: Scenario 1                               | 53 |

| 3.9  | Blocking versus Deadlock Detection: Scenario 2                               | 53 |

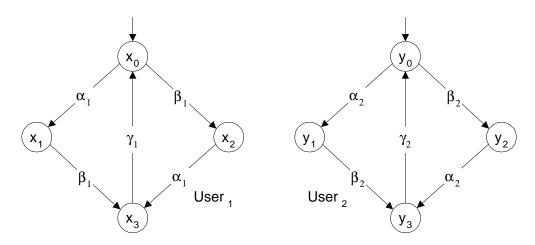

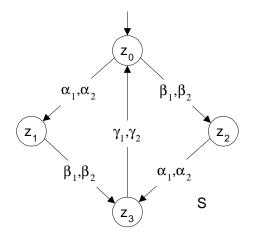

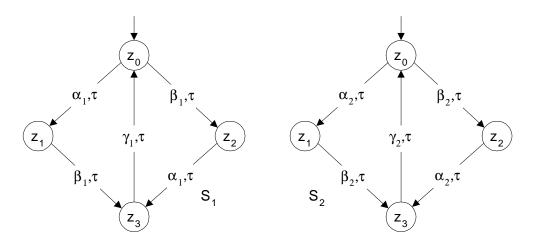

| 3.10 | Two Users Competing for Resources                                            | 54 |

| 3.11 | Resource Sharing Specification for Users                                     | 54 |

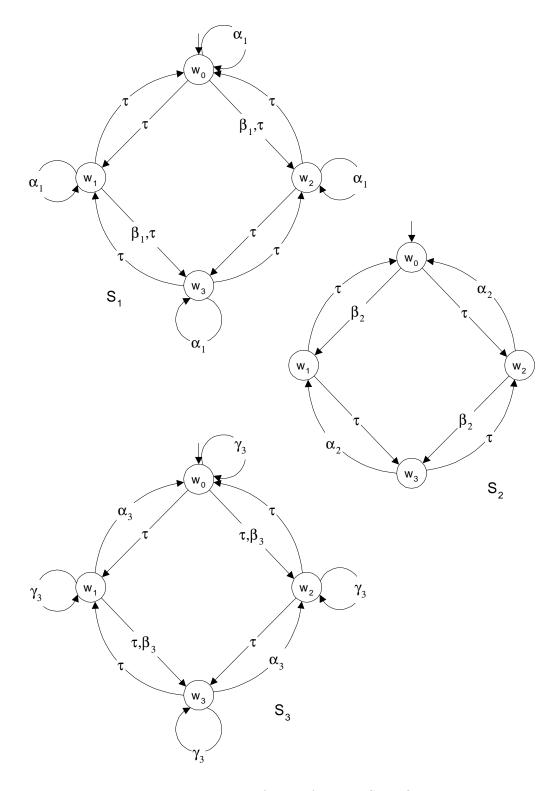

| 3.12 | Distribution of Resource Sharing Specification                               | 55 |

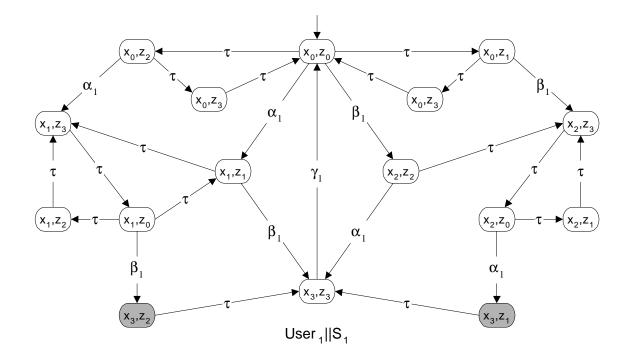

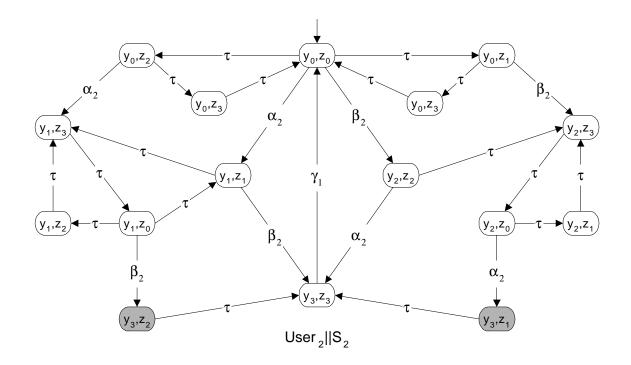

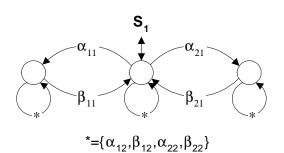

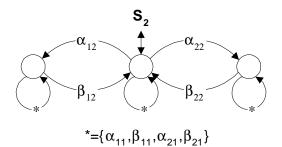

| 3.13 | $User_1    S_1$ and $User_2    S_2$                                          | 56 |

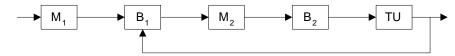

| 3.14 | A Transfer Line                                                              | 57 |

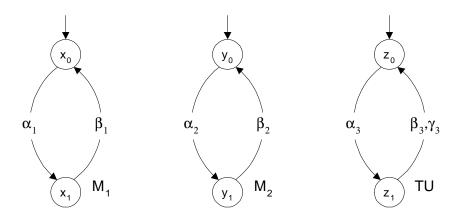

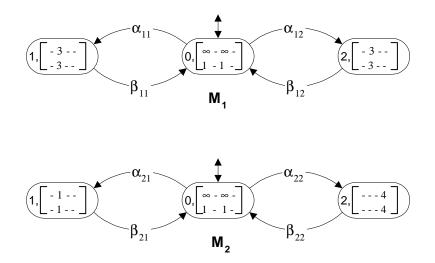

| 3.15 | Transfer Line Components                                                     | 58 |

| 3.16 | Transfer Line Under/Overflow Specification                                                                                     | 59  |

|------|--------------------------------------------------------------------------------------------------------------------------------|-----|

| 3.17 | Distribution of Transfer Line Specification                                                                                    | 60  |

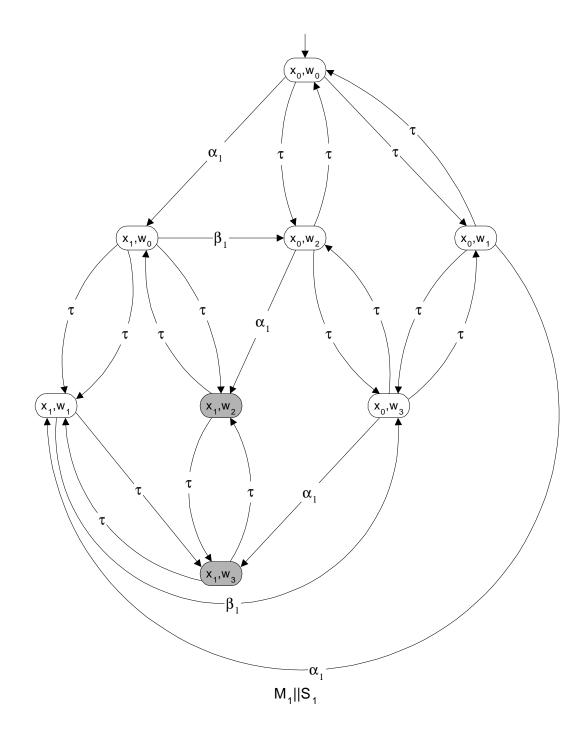

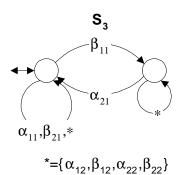

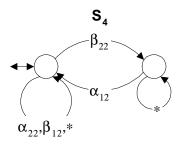

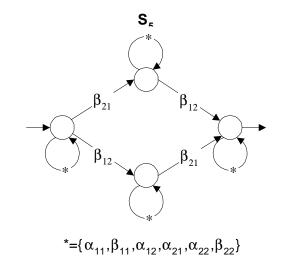

| 3.18 | $M_1 \  S_1 \dots \dots$ | 61  |

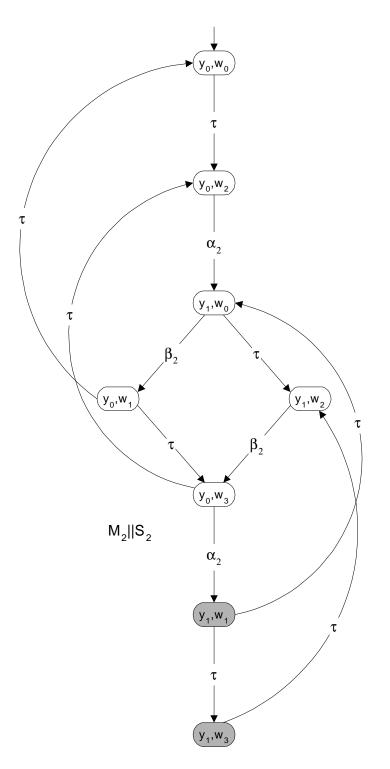

| 3.19 | $M_2 \  S_2 \dots \dots$ | 62  |

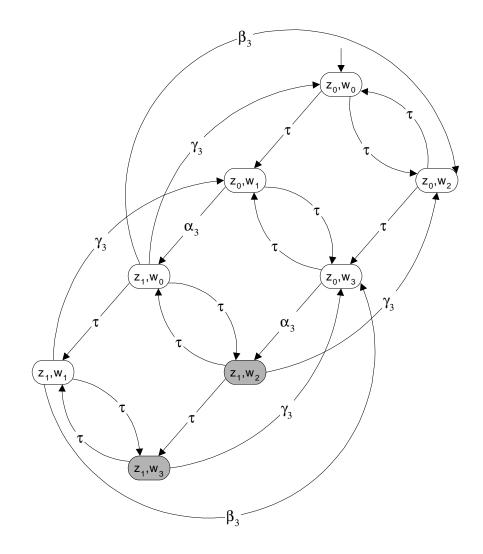

| 3.20 | $M_3 \  S_3 \dots \dots$ | 63  |

| 3.21 | Deadlock removing control action may cause deadlock                                                                            | 65  |

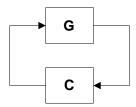

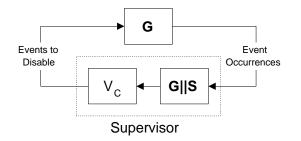

| 4.1  | Supervisory Control Setup                                                                                                      | 79  |

| 4.2  | Supervisory Control Setup for the Proposed Scheme                                                                              | 80  |

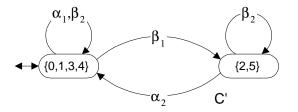

| 4.3  | Reduction in Specificity by Merging States                                                                                     | 86  |

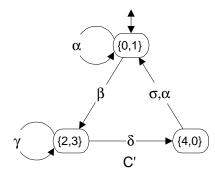

| 4.4  | A Smaller Factory                                                                                                              | 93  |

| 4.5  | Buffer Under/Overflow Spec for the Smaller Factory                                                                             | 93  |

| 4.6  | A Supervisor for the Smaller Factory                                                                                           | 93  |

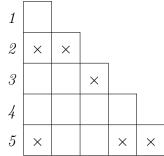

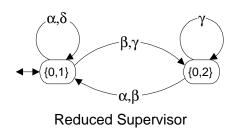

| 4.7  | A Reduced Supervisor for the Smaller Factory                                                                                   | 96  |

| 4.8  | Supervisor Cannot be Reduced by a Partition                                                                                    | 98  |

| 4.9  | Supervisor Reducible using a Cover                                                                                             | 98  |

| 4.10 | Conservative Lower Bound Estimation                                                                                            | 101 |

| 4.11 | A Minimal Supervisor whose Estimate is Conservative                                                                            | 102 |

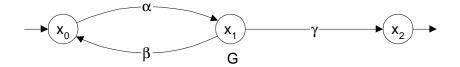

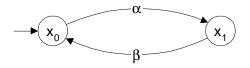

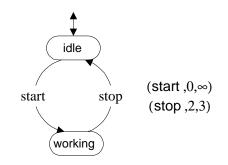

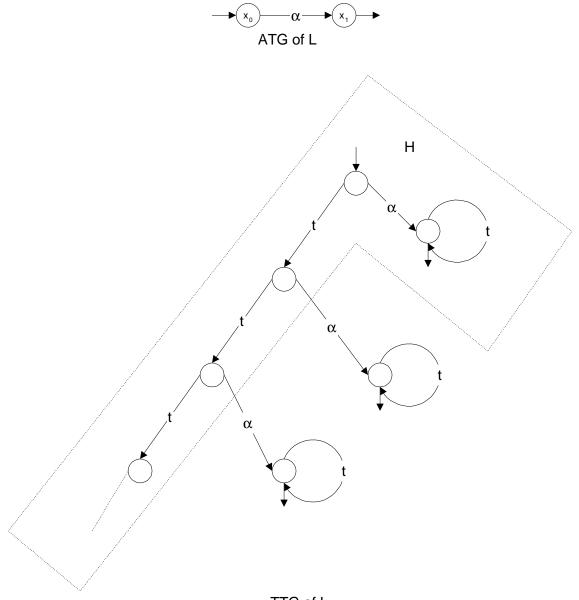

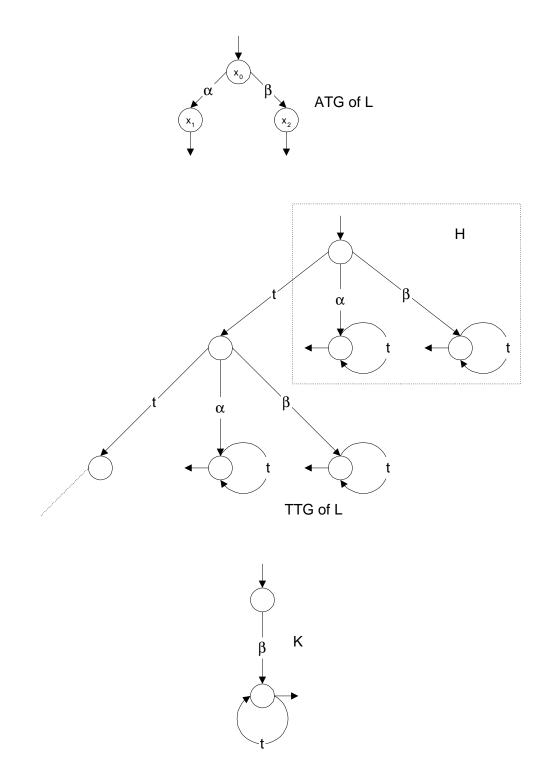

| 5.1  | ATG of a Simple Machine                                                                                                        | 109 |

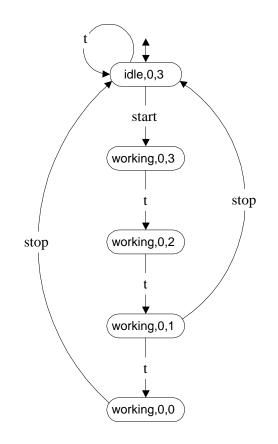

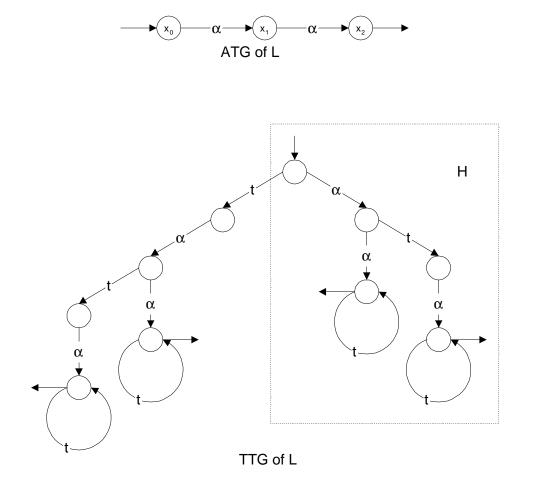

| 5.2  | Timed Transition Graph of a Simple Machine                                                                                     | 114 |

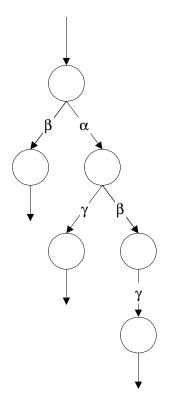

| 5.3  | Activity Transition Graph of $G$                                                                                               | 117 |

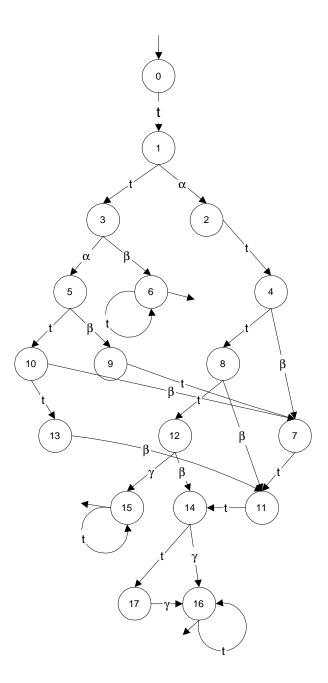

| 5.4  | Timed Transition Graph of $G$                                                                                                  | 118 |

| 6.1  | Counter-example: ATG                                                                                                           | 151 |

| 6.2  | Counter-example: Partial TTG                                                                                                   | 152 |

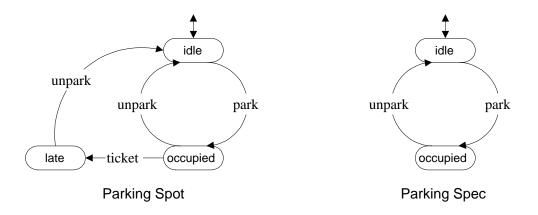

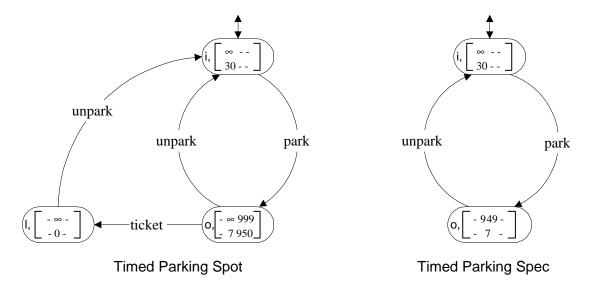

| 7.1  | A Car Parking Setup and Specification                                                  | 159 |

|------|----------------------------------------------------------------------------------------|-----|

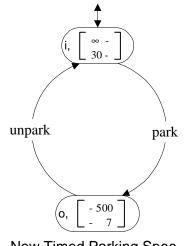

| 7.2  | BW Not Closed Under Control: Scenario 1                                                | 160 |

| 7.3  | BW Not Closed Under Control: Scenario 2                                                | 162 |

| 7.4  | BW Not Closed Under Control: Scenario 3                                                | 163 |

| 7.5  | A timer graph that is not proper                                                       | 169 |

| 7.6  | A proper timer graph                                                                   | 170 |

| 7.7  | A timed generator                                                                      | 171 |

| 7.8  | An explicit timed interpretation of a timed generator                                  | 172 |

| 7.9  | Timed Generator for the Parking Spot                                                   | 183 |

| 7.10 | Temporal Specification for Parking Setup                                               | 185 |

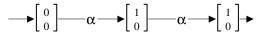

| 7.11 | Timed Generator for the Scenario of Example 116                                        | 185 |

| 7.12 | Timed Generator for the Parking Specification                                          | 189 |

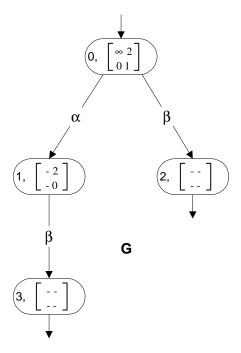

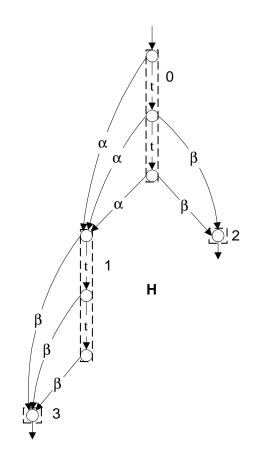

| 7.13 | Timed Generator that generates $L$ of Example 118 $\ldots \ldots \ldots \ldots \ldots$ | 190 |

| 7.14 | Timed Generator that generates $H$ of Example 118 $\ldots \ldots \ldots \ldots \ldots$ | 190 |

| 7.15 | Reason for setting $m_{\sigma}$ : ATG                                                  | 193 |

| 7.16 | Reason for setting $m_{\sigma}$ : TTG                                                  | 194 |

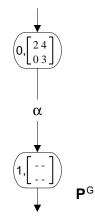

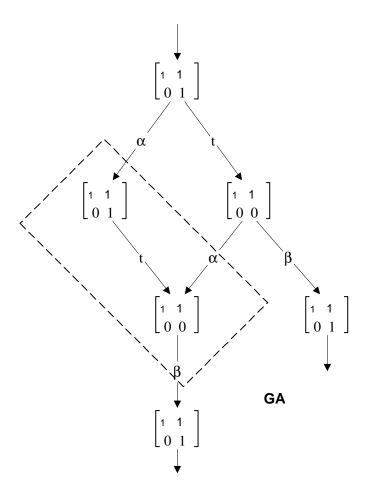

| 7.17 | ATG A for which an equivalent TG is to be found                                        | 194 |

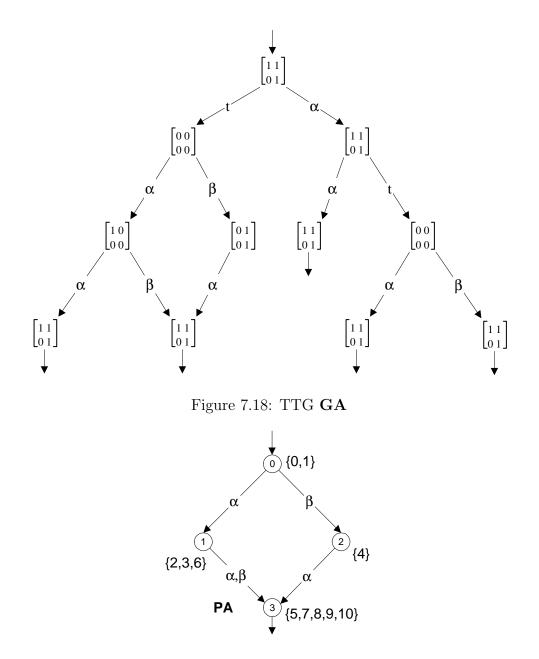

| 7.18 | TTG GA                                                                                 | 195 |

| 7.19 | TATG <b>PA</b>                                                                         | 195 |

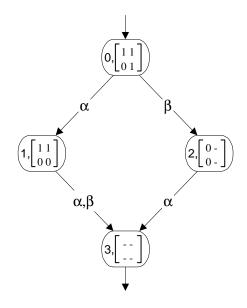

| 7.20 | Derived Timed Generator $\mathbf{G}$                                                   | 196 |

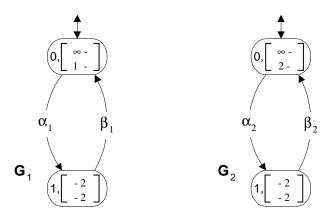

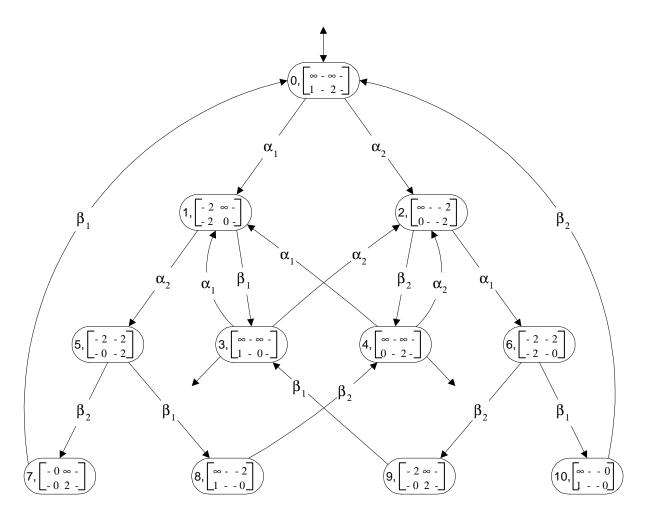

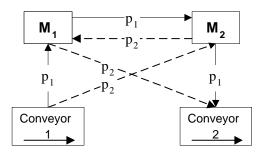

| 7.21 | A Simple Factory Setup                                                                 | 199 |

| 7.22 | Component Machines of the Simple Factory                                               | 199 |

| 7.23 | Synchronous Composition of $\mathbf{G}_1$ and $\mathbf{G}_2$                           | 200 |

| 7.24 | Under/Overflow Specification                                                           | 201 |

| 7.25 | Maximal Behaviour of the Small Factory subject to the Under/Overflow Spec              | 202 |

| 7.26 | Temporal Specification for the Small Factory   | 203 |

|------|------------------------------------------------|-----|

| 7.27 | A Manufacturing Cell                           | 204 |

| 7.28 | Manufacturing Cell: $M_1$ and $M_2$            | 205 |

| 7.29 | Manufacturing Cell: Behavioural Specifications | 206 |

# 1. INTRODUCTION

#### Yes, but are they practical?

This is a refrain that is heard a bit too often regarding the modelling and control of discrete event systems. A discrete event system (DES) is a physical system that is discrete (in time and space), asynchronous (event-driven rather than clock-driven), and in some sense generative (or nondeterministic) [Won01]. Ramadge and Wonham have provided an automaton based framework [RW82] (called RW) for the modelling and control of DES. Over the past couple of decades a great deal of literature has been published in this area. It has been shown that a DES can be controlled in a systematic and optimal manner [RW87a], [RW87b], [RW89]; modular [WR88], [WW98] and hierarchical [Zh092], [ZW90], [WW96a], [WW96b], [Pu00] decomposition schemes have been proposed; time has been incorporated into RW [OW90], [Bra93], [BW94], [LW88], [O'Y91] to expand its modelling capabilities. And yet the refrain is heard. The main reason for this is the state explosion problem. Most complex systems are composed of several interacting components. The state space of such a system is usually represented by the cross product of the state sets of the individual components. As a result, the state space may grow exponentially with the number of interacting components.

Modular and hierarchical decomposition schemes can often provide a stepwise approach for handling complex systems. But we end up dealing with the entire state space at one stage or the other. In the hierarchical scenario, a control action computed at the high (abstract) level has to be implemented at the low (physical) level. This implementation often requires complete knowledge of the low level state space. In the modular scenario, the control tasks can be broken down but the state space of the physical system still needs to be computed.

The situation is even worse if time is modelled explicitly. In addition to the complexity due to the interaction of components, there is complexity due to the modelling of time. Thus the state space of a timed system is usually much bigger than that of an untimed system. The flexibility of incorporating temporal information usually exacts a big price in terms of the complexity of the state space.

### 1.1. Goal and the Main Results

The main goal of this thesis is to make a contribution towards providing practical tools and methods for the modelling and control of discrete event systems. We aim to tackle the state explosion problem in discrete event systems. Towards that end, we first present a supervisory control design method for composite systems such that the complete state space never needs to be computed. The proposed method is symbolic in nature: a control function is provided that can be efficiently evaluated to compute the control action at any given state. This method is prone to blocking but can be augmented to provide deadlock avoidance. Supervisor synthesis is an NP-hard problem [GW00] even when blocking is not an issue. Under that backdrop, our proposed scheme provides an efficient synthesis tool under reasonably mild restrictions.

Sometimes it may not be practical to use our symbolic scheme. Among other reasons, this may happen either because the preconditions for symbolic supervision are violated or because blocking is a concern. For such scenarios, we present a heuristic supervisor

#### 1.2. RELATED WORK

reduction algorithm. A supervisor reduction algorithm is meant to reduce the state size of the automaton (or the entries in a lookup table) that is used for controlling a physical system. It is always possible to find a minimal supervisor for a given job but the problem is NP-hard [SW01]. Our algorithm does not attempt to find a minimal supervisor. In fact, it does not even guarantee a reduced supervisor. However it seems to perform quite well in practice.

Finally we present a compact model of timed discrete event systems (TDES). Rather than using a special event to model the passage of time, we use timers instead. These timers countdown with respect to a global clock. This allows us to compactly incorporate temporal information. The model is also quite robust to changes in time scale. In other words, the size of the model usually does not increase much if the frequency of the global clock is increased. But the main advantage of the proposed model is that it is closed under control. A TDES subject to supervisory control can be modelled as another TDES. This is a very desirable property since it allows us to perform a series of control designs on a TDES.

### 1.2. Related Work

In this section we outline some of the related work done by other researchers. We begin with symbolic methods in discrete event systems. Most of it is quite different than our approach but the basic idea is the same: avoid enumerating the state space. Then we move on to supervisor reduction which has not been a very active area since the publication of [VW86]. It is shown in [VW86] that finding a minimal supervisor is exponential in time and that has perhaps retarded research in this area. The problem becomes a lot more tractable if the aim is simply to find a reduced supervisor rather than a minimal supervisor. Finally

#### 1.2. RELATED WORK

we outline the related work in timed discrete event systems.

#### 1.2.1. Symbolic Supervision

Symbolic methods have long been used for model checking and verification of properties of discrete event systems [McM92], [BCM92], [CGP01]. These methods try to exploit inherent regularities and symmetries in the system being verified and are often used for the verification of large digital hardware systems. The system representation is based on boolean decision diagrams (BDDs) [Ake78], [Bry86] which are used to represent binary functions. A large class of boolean functions can be represented by function graphs whose size is a polynomial function of the number of boolean variables. Thus BDDs can often compactly represent systems that are rich in symmetry although the size of a BDD is sensitive to the variable ordering [Bry86]. The inability of BDDs to represent general functions prevented their direct application in the field of supervisory synthesis although one such approach is presented in [HWT92b], [HWT92a].

Integer decision diagrams (IDDs) [Gun97] are an extension of BDDs that can be used to represent general finite functions. IDDs utilize the structure of integers and arithmetic operations and share a number of characteristics with BDDs. In particular, IDDs can be used to provide a compact representation of discrete event systems. IDDs have been successfully used in [Zha01] for the purpose of supervisor synthesis: a supervisor has been synthesized for a system with state size of  $1.96 \times 10^{15}$ .

The common theme of all the aforementioned results is that they use some sort of a decision diagram to construct the system model. The reduction in computational complexity is a direct result of the properties of the decision diagram. Heuristics are used to automatically get a *good* variable ordering; these heuristics are often quite good for loosely coupled systems. All the computations are still carried out offline and herein lies the major

5

weakness of these methods: the results need to be stored somewhere. As the state space increases so does the complexity of computing the control action and the complexity of storing it. The approach we take in this thesis is an online approach. We compute the control action whenever it is needed (upon entering a new state). The reduction in complexity is not a result of a particular representation (BDD, IDD etc) but of a decomposition defined on the system. This decomposition allows us to distribute the control task and employ a *look-ahead* control. To the best of our knowledge, no one else has used a similar decomposition. However a look-ahead policy has been implemented in [CLL92a], [CLL92b]. The authors there employ a look-ahead window of fixed size (say N). The control action at the current state is based on what can be foreseen in the next N steps. An assumption is made regarding the system behaviour beyond those N steps. The assumption can be *optimistic*: if nothing bad can be foreseen in N steps then it is assumed that nothing bad will happen after that; the assumption can be *conservative*: if safety cannot be guaranteed based on a look-ahead of N steps then it is assumed safety is in jeopardy after that. The authors present a lower bound on N that guarantees that the control is optimal (i.e. the same as in the case when all the information is available). However, in general, this bound cannot be computed without constructing the entire state space. Thus the choice of N is arbitrary and a designer must rely on intuition about the system behaviour.

A symbolic synthesis approach based on predicates is presented in [AMP95]. There the authors have presented supervisory control setup in a game theoretic framework. The aim is to find winning strategies without enumerating the entire state space. Similar work in a control theoretic framework is presented in [Ma02]. While similar in spirit, their approach is quite different than ours.

#### 1.2.2. Supervisor Reduction

Given a plant and a supervisor, the supervisor reduction problem is to find a supervisor that has fewer states than the original supervisor but performs the same control task. A reduced supervisor is typically found by inducing it from a suitable cover [VW86] of the state set of the original supervisor. It is shown in [VW86] that it is always possible to find a minimal supervisor (there may be more than one). It can be done by simply enumerating all possible (and suitable) covers and picking a minimal one. However this is very inefficient; in fact, finding a minimal supervisor is NP-hard [SW01]. A supervisor reduction algorithm is presented in [SW00], [SW01]. This work recognizes the fact that is perhaps futile to search for an efficient algorithm that produces a minimal supervisor. So it focuses on finding just a reduced supervisor instead. A suitable congruence is defined on the state set of the original supervisor. This congruence leads to a partition of the state set and a supervisor is induced from that partition. A partition of a set can have no more elements than the set so this always leads to a reduced supervisor. Our algorithm provides no such guarantees as it induces the supervisor from a cover (which can have more elements than the set of which it is a cover). However we use a greedy heuristic that is based on similar heuristics used for finding an approximate set cover [Chv79], [Hoc82]. These set cover heuristics provide good approximate solutions to the set cover problem. Since the problem of finding a control cover is quite similar to finding a set cover, we expect our algorithm to perform well in practice. In fact, the algorithm has been able to produce reduced supervisors for a large variety of systems.

#### 1.2. RELATED WORK

#### 1.2.3. Timed Discrete Event Systems

The RW framework proposed by Ramadge and Wonham in [RW82] does not model time explicitly. It is possible to make statements like "The machine must be turned on *before* a workpiece can be processed" but it is not possible to infer *when* the machine is turned on. Thus we can only talk about the relative order of occurrences of various events. The work presented in [Mol86] extends RW to include temporal information by assigning time delays to events. The effect of time delays for supervisory control is explored in [LW88].

Brave and Heymann use a timer to model time in [BH88]. The timer is reset to zero upon entering a state and starts counting up with respect to a global clock. Time intervals are assigned for the possible occurrence of events and nondeterminism is resolved using the current timer value. The composition of systems is problematic in this setup but our proposed model is very close to this in spirit. We use timers as well but composition is well defined in our framework.